ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

## DESIGN OF A LOW POWER CONSUMING SRAM CELL USING MINIMUM TRANSISTORS IN FINFET TECHNOLOGY

## Rajinder Singh\*, Shelly Kalra

\*Research Scholar, Ludhiana College of Engineering & Technology, Ludhiana Assistant Professor, Ludhiana College of Engineering & Technology, Ludhiana

DOI: 10.5281/zenodo.268684

#### **ABSTRACT**

Power leakage in a RAM cell is a major concern in today's development of shrinking size and high standby memories. To solve the power leakage problem, many researchers have proposed different ideas from the device level to the architectural level and above. SRAM designs has become the issue of significant research to increase require for laptops, integrated circuit (IC) memory cards, notebooks and hand held communication devices. This article is based on the motivation of reduction of the average leakage power in SRAM memory cell in the 6T, 7T, 8T and 9T in FINFET technology at 22.5nm by using the Tanner tool which is having a supply voltage of 1.7 volts. The circuit verification is done on the Tanner tool, Schematic of the SRAM cell is designed on the S- Edit and net list simulation done by using T-spice and waveforms are analyzed through the W-edit.

KEYWORDS: CMOS Logic, Low power, Speed, SRAM and VLSI.

### INTRODUCTION

The SRAM is the most commonly used block in Digital Signal Processing (DSP), therefore its performance and power optimization is of utmost importance for storing the data. With the technology scaling to deep sub-micron, the speed of the circuit increases rapidly. At the same time, the power consumption per chip also increases significantly due to the increasing density of the chip. Therefore, in realizing modern Very Large Scale Integration (VLSI) circuits, low-power and high-speed are the two predominant factors which need to be considered. Like any other circuits' design, the design of high-performance and low-power SRAM can be addressed at different levels, such as architecture, logic style, layout, and the process technology. As the result, there always exists a trade-off between the design parameters such as speed, power consumption, and area.

Arithmetic circuits, like SRAM, adders and multipliers, are one of the basic components in the design of communication circuits. Recently, an overwhelming interest has been seen in circuit and hence affects the performance of the device.

Very Large Scale Integration (VLSI) includes wadding large number of electronics devices into lesser areas. VLSI is the process of integrating or merging hundreds of thousands of transistors on a single silicon semiconductor microchip. VLSI technology was considered in the late 1970s when advanced level computer processor microchips were under development.

#### BASIC ARCHITECTURE AND WORKING OF SRAM

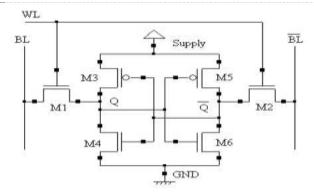

Figure shows the write mode of conventional SRAM cell. Word line is used for enabling the access transistors M1 and M2 for write operation. BL and ¯BL lines are used to store the data and its compliment. For write operation one BL is High and the other bit line on low condition.

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

Figure 1.1 Conventional 6T SRAM Cell [1]

For writing "0" BL is Low and BL is high. When there is an assertion of the word line high transistor M1 and M4 is on and any charged stored in the BL goes through M1- M4 path to ground. Due to Zero value at Q the M5 transistor is ON and M6 is OFF so the charged stored at Q. bar line. Similarly in the write "1" operation BL is high due to this M6 is ON and the charge store on is discharged through the M2-M6 path and due to this low value on the M3 is ON and M4 is OFF so the charged stored on the Q.

Memory Architecture is Random-access architecture which is an Asynchronous design. The name is derived from the fact that memory locations (addresses) can be accessed in random order at a fixed rate, independent of physical location, for reading or writing. The storage array, or core, is made up of simple cell circuits arranged to share connections in horizontal rows and vertical columns. The horizontal lines, which are driven only from outside the storage array, are called word lines, while the vertical lines, along which data flow into and out of cells, are called bit lines. A cell is accessed for reading or writing by selecting its row and column. Each Cell can store 0 or 1. Memories may simultaneously select 4, 8, 16, 32, or 64 columns in one row depending on the application. The row and column (or groups of columns) to be selected are determined by decoding binary address information. For example, consider a row decoder that has 2 n out-put lines, a different one of which is enabled for each different n-bit input code. The column decoder takes m inputs and produces 2 m bit line access signals, of which any of them can be enabled at one time. The bit selection is done using a multiplexer circuit to direct the corresponding cell outputs to data registers. In total, 2 n X 2 m cells are stored in the core array. In this design, the number of rows and columns, both are equal to 64 for 4Mb memory cut. Using two such memory cuts, a 8Mb SRAM memory is designed. The SRAM IC is R/W memory circuit that permits the modification (writing) of data bits to be stored in a memory array, as well as their retrieval (reading). The SRAM IC was developed using the CDS IC446, cadence IC design environment. The design was based on the AMI 0.6-micron process. The SRAM IC design consists of SRAM cells, pre charge, sense amplifiers, MUX, NAND gates, AND gates, NOR gates and row Decoder. The most important part is the cell as all the other circuitry is connected to and around the cell. The popular, full CMOS 6-transistor cell configuration was used to design the SRAM memory array. Some of the advantages of using full CMOS SRAM configuration are low static power dissipation, superior noise margins, high switching speeds and suitability for high-density SRAM arrays. In order to design a 64 bit SRAM, 64 full CMOS 6-T cells were used. Each full CMOS 6-T cell has a capability of storing 1 bit.

As per the Literature review it is concluded that there is lot of work done for the reduction of dynamic power dissipation and also there are research paper which is targeting the static power dissipation. As the technology goes down the power dissipation becomes the main design criteria in SRAM memory design. Because memory will decides the total power dissipation. Based on the above literature survey and after carefully analyzing the previous work that is optimized the short circuit power dissipation in SRAM memory cell. Based on the literature survey it is concluded that SRAM memory cell dissipate large amount of short circuit power during rise time and fall time of input data because at that time the direct path exist between the  $V_{dd}$  and ground in a single cell the short circuit power is micro watt range at 90 nm technology as the size of memory increases the amount of power increases corresponding .so based on the previous work it has been decided to optimize the short circuit power.

Static random access memory (SRAM), the most widely used embedded memory, typically occupies the largest portion of SoC die area, and often dominates the total chip power. In order to maintain performance, however, this has required a corresponding reduction in the transistor oxide thickness to provide sufficient current drive at

[Singh\* *et al.*, 6(5): May, 2017] IC<sup>TM</sup> Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

the reduced supply voltages. To further reduce the leakage current, the stacking effect is used by switching off the stack transistors when the memory is ideal. The transistors have been lowered which also contributes to leakage currents and reduces the battery life dramatically. The low power reduction techniques reduce the leakage based on the dependencies of the tunneling currents on the terminal voltages, the gate oxide thickness, and the type of the transistor. Various efficient techniques which gives overall best performance over existing SRAM design approaches that allow the analysis and simulations of different parameters at 90nm and 45nm technology successfully on the basis of the power dissipation, speed and their temperature dependence with the area efficiency of the circuit.

## POWER CONSUMPTION IN CMOS CIRCUITS

There are three main components of power consumption in digital CMOS VLSI circuits.

- 1) Switching Power: consumed in charging and discharging of the circuit capacitances during transistor switching.

- 2) Short-Circuit Power: consumed due to short-circuit current flowing from power supply to ground during transistor switching. This power more dominates in Deep Sub Micron (DSM) technology.

- 3) Static Power: consumed due to static and leakage currents flowing while the circuit is in a stable state. The first two components are referred to as dynamic power, since power is consumed dynamically while the circuit is changing states. Dynamic power accounts for the majority of the total power consumption in digital CMOS VLSI circuits at micron technology [15], [16].

$$P_{avg} = P_{Switching} + P_{Short\text{-}Circuit} + P_{Leakage}$$

$$=(\alpha_0 \rightarrow_I \times C_L \times V_{dd}^2 \times f_{clk}) + (I_{sc} \times V_{dd}) + (I_{leakage} \times V_{dd})$$

## SCHEMATIC OF LOW POWER SRAM CELL

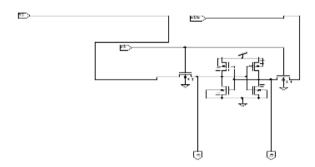

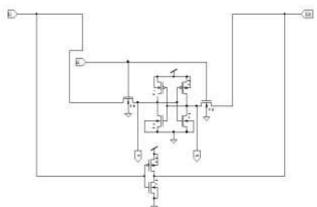

Below Figures are of 1 Bit SRAM Cell using 6T, 7T & 8T shows the write mode of low power SRAM cell. Word line is used for enabling the access transistors M1 and M2 for write operation. BL and  $\overline{BL}$  lines are used to store the data and its compliment. For write operation one BL is High and the other bit line on low condition. In low power SRAM cell, introduced one Control signal transistor for controlling these transistors. But due to one more transistors area for low power SRAM cell is increased in comparison to Conventional approach. This control transistor uses control select signals which can be properly control the short circuit power dissipation. During write operation this transistor which has control signal works as in on condition. During read operation it will remain in off condition. When this transistor is in off condition will break the path which is in between  $V_{dd}$  and Ground.

Figure 3.1 6-T SRAM cell

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

Figure 3.2 7-T SRAM cell

In above figure 3.2, the transistor present at the ground prevents the short circuit of supply voltage when accidently bl and blb has same values. Although this condition is invalid and should be prevented to occur.

Figure 3.3 8-T SRAM cell\

In above 8T SRAM cell, the condition that bl and blb of same value, is totally avoided. There is a NOT gate present between bl and blb such that the condition of equivalency of both may never exist even for a shorter period of time.

## **FINAL RESULT**

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

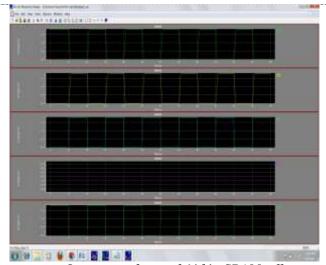

Output waveforms of 64-bits SRAM cell

The above figure shows the output waveforms of 1-bit 6T SRAM cell. The output waveforms of all circuits look like same. But power and delay are the difference between them as shown in below table.

#### Performance parameters of Different SRAM Cell

| Design     | Minimum Leakage<br>Power | Average Leakage<br>Power |

|------------|--------------------------|--------------------------|

| 6T         | 0.0023nW                 | 9.4943μW                 |

| <b>7</b> T | 0.0032nW                 | 8.321µW                  |

| PG8T       | 0.0019nW                 | 0.61μW                   |

#### Comparison of PG8T with other Technologies

| 8T     | CP10T               | PPN10T | PG9T   | PG8T   |

|--------|---------------------|--------|--------|--------|

| 1 33µW | 0.73uW              | 0.77µW | 0.74uW | 0.61µW |

|        | <b>8T</b><br>1.33μW |        |        |        |

In the above comparison with the literature, it is seen that the designed 8T SRAM cell saves 18% of the power as compared to 9T SRAM Cell. Moreover the number of transistors used is one less than the literature. Hence considering the area covered, nearly 12% is saved while using 8T technology.

#### **CONCLUSION**

The design and implementation of the SRAM memory is shown in this paper. In this paper the design of 6T, 7T & 8T SRAM memory cell is shown. The total power consumption is also significantly lower as compared to the existing papers based on SRAM. So according to the requirement these SRAM memory cells can be used in internal CPU. The low power operation is achieved without sacrificing performance of memory. Power consumption is a function of load capacitance, frequency of operation, and supply voltage. A reduction of any one of these is beneficial. A reduction in power consumption provides several benefits. Less heat is generated, which reduces problems associated with high temperature, such as the need for heat sinks. This provides the consumer with a product that costs less. Furthermore, the reliability of the system is increased due to lower-temperature stress gradients on the device. An additional benefit of the reduced power consumption is the extended life of the battery in battery-powered systems. In this paper it is concluded that power dissipation and delay are less than the base paper.

ISSN: 2277-9655 **Impact Factor: 4.116** ICTM Value: 3.00 **CODEN: IJESS7**

#### REFERENCES

- [1] Prashant Upadhyay and Mr. Rajesh Mehra, "Low Power Design of 64-bits Memory by using 8-T Proposed SRAM Cell", International Journal of Research and Reviews in Computer Science (IJRRCS), Vol. 1, No. 4, December 2010.

- [2] Sreerama Reddy G.M, P. Chandrashekara Reddy, "Design and VLSI Implementation of 8 Mb Low Power SRAM in 90nm", European Journal of Scientific Research ISSN 1450-216X, Vol.26 No.2 (2009), pp.305-314.

- [3] Keejong Kim, Hamid Mahmoodi, "A Low-Power SRAM Using Bit-Line Charge-Recycling", IEEE Journal of Solid State Circuits, Vol. 43, No. 2, February 2008.

- [4] Yung-Do Yang and Lee-Sup Kim, "A Low-Power SRAM Using Hierarchical Bit Line and Local Sense Amplifiers" IEEE Journal of solid state circuits, Vol.40, No. 6, June 2005.

- [5] Chang, Y., Lai, F. and Yang, C., "Zero-aware asymmetric SRAM cell for reducing cache power in writing zero", IEEE Trans. VLSI Systems, Vol. 12, no. 8, pp. 827-36,2004.

- [6] Aly, R., Faisal, M. and Bayoumi, A., "Low-power cache design using 7T SRAM cell" in Proc. IEEE System on Chip Confrence, pp. 171-174, 2005.

- [7] Neil H.E.Weste, David Harris, Ayan Banerjee "CMOS VLSI Design, Pearson Education, third Edition, pp. 55-57.

- [8] Ken Martin, "Digital Integrated Circuit Design"

- [9] Varun Kumar Singhal, Balwinder Singh, "Comparative study of power reduction techniques for Static random access memory" International Journal of VLSI and Signal Processing Applications, Vol. 1, Issue 2, May 2011,(80-88), JSSN 2231-3133

- [10] Irina Vazir, Prabhjot S. Balaggan, Sumandeep Kaur, Cailan Shen, "SRAM IP for DSP/SoC Projects" San Jose State University SRAM

- [11] Ashish Siwach, Rahul Rishi," IJCEM International Journal of Computational Engineering & Management, Vol. 11, January 2011.

- [12] Texas Instruments, "CMOS Power Consumption and Cpd Calculation" SCAA035B June 1997

- [13] Debasis Mukherjee1, Hemanta Kr. Mondal2 and B.V.R. Reddy3, "Static Noise Margin Analysis of SRAM Cell for High Speed Application" IJCSI International Journal of Computer Science Issues, Vol. 7, Issue 5, September 2010

- [14] Shilpi Birla, Neeraj Kr. Shukla, Manisha Pattanaik, R.K.Singh, Device and Circuit Design Challenges for Low Leakage SRAM for Ultra Low Power Applications" Canadian Journal on Electrical & Electronics Engineering Vol. 1, No. 7, December 2010.

- [15] Benton H. Calhoun, Member, IEEE, and Anantha P. Chandrakasan, Fellow, IEEE, "Static Noise Margin Variation for Sub-threshold SRAM in 65-nm CMOS" IEEE Journal of Solid State Circuits, Vol. 41, No. 7. July 2006.

- [16] N.M. Sivamangai1 and K. Gunavathi2, Non-members, "A Low Power SRAM Cell with High Read Stability" ECTI Transaction of Electronics and Communication, Vol.9, No.1 February 2011.

- [17] Srinivasa Rao, Raghavendra Sirigiri, V. Malleswara Rao, "New Technique for reducing Sub-Threshold leakage in SRAM" International Journal of Engineering Sciences Research-IJESR may 2011.

## CITE AN ARTICLE

Singh, R., & Kalra, S. (2017). DESIGN OF A LOW POWER CONSUMING SRAM CELL USING MINIMUM TRANSISTORS IN FINFET TECHNOLOGY. INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY, 6(5), 562-567. doi:10.5281/zenodo.268684